搜尋

- 04/24/2023

系統級封裝(SiP) : 一站式微小化解決方案

半導體元件隨著各種消費性通訊產品的需求提升而必須擁有更多功能,元件之間也需要系統整合。因應半導體製程技術發展瓶頸,系統單晶片(SoC)的開發效益開始降低,異質整合困難度也提高,成本和所需時間居高不下。此時,系統級封裝(SiP)的市場機會開始隨之而生。

採用系統級封裝(SiP)的優勢

USI 環旭電子一站式微小化解決方案

相較於SoC製程,採用系統級封裝(SiP)的最大優勢來自於可以根據功能和需求自由組合,為客戶提供彈性化設計。以最常見的智慧型手機為例,常見的的功能模組包括傳感器、Wi-Fi、BT/BLE、RF FEM、電源管理晶片…等。而系統級封裝即是將這些獨立製造的晶片和元件共同整合成模組,再從單一功能模組整合成子系統,再將該系統安裝到手機系統PCB上。

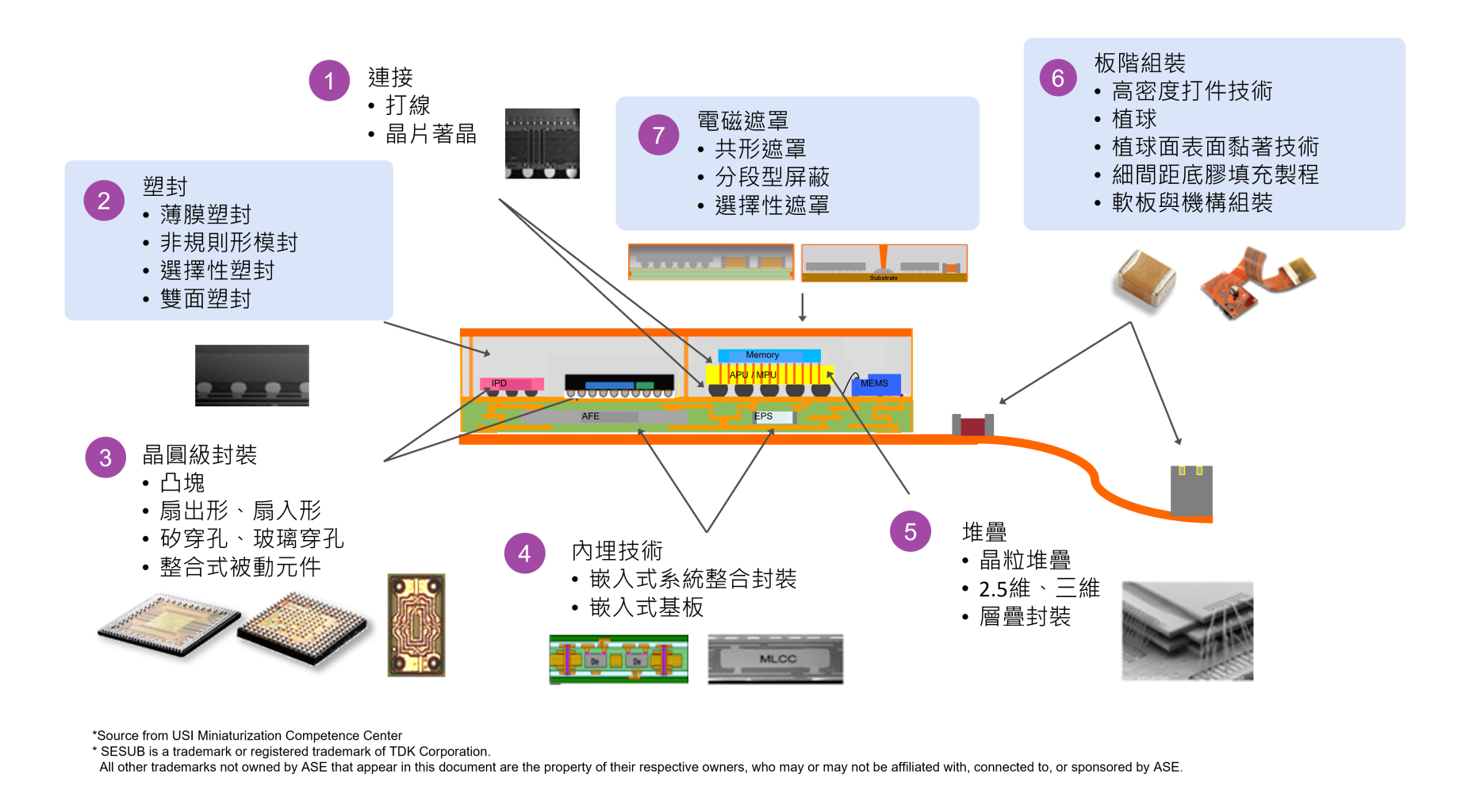

SiP整體製程囊括了著晶、打線、主/被動元件SMT及塑封技術,封裝成型可依據客戶設計製作不同形狀模組,甚至是3D立體結構,藉此可將整體尺寸縮小,預留更大空間放置電池,提供更大電力儲存,延長產品使用時間,但功能更多、速度更快,因此特別適用於射頻相關應用如5G毫米波模組、穿戴式裝置及汽車電子等領域。

延伸閱讀:【微小精確、事半功倍】Ep.3 生活中的微小化應用

微小化製程三大關鍵技術

在設計中元器件的數量多寡及排布間距,即是影響模組尺寸的最主要關鍵。要能夠實現微小化,最重要的莫過於三項製程技術:塑封、遮罩及高密度打件技術。

系統級封裝(SiP)製程關鍵技術

高密度打件

在高密度打件製程方面,環旭電子已達到約為嬰兒髮絲直徑的40μm。以10x10被動元件陣列做比較,大幅縮減超過70%的主板面積,其中的40%乃源自於打件技術的突破。

塑封

由於高密度打件採用微小化元器件與製程,因此元器件與載板之間的連結,吃錫量大幅減少,為提高打件可靠度,避免外界濕度、高溫及壓力等影響,塑封製程可將完整的元器件密封包覆在載板上。相較於一般委外封測(OSAT)塑封約100顆左右,環旭電子的系統級封裝塑封技術,則是可容納高達900顆組件。

「共形」及「分段型」屏蔽

另一方面,系統級封裝模組需要高密度整合上百顆電子元件,同時避免與PCB主板上其他元件相互干擾。此外,在模組外部也必須解決相同的干擾問題。因此,必須透過一項重要製程來形成元件之間的屏障,業界稱之為共形屏蔽(Conformal Shielding)和分段型屏蔽(Compartment Shielding)。

在業界普遍常見的金屬屏蔽罩,每一段均需要保留約1mm寬度的焊盤與排除區域 (Keep-Out Zone),環旭電子的共形及分段型屏蔽僅需10%的寬度。以一個多頻4G模組為例,可為其他元件騰出超過17%的空間,並可屏蔽40-50 dB的電磁干擾。

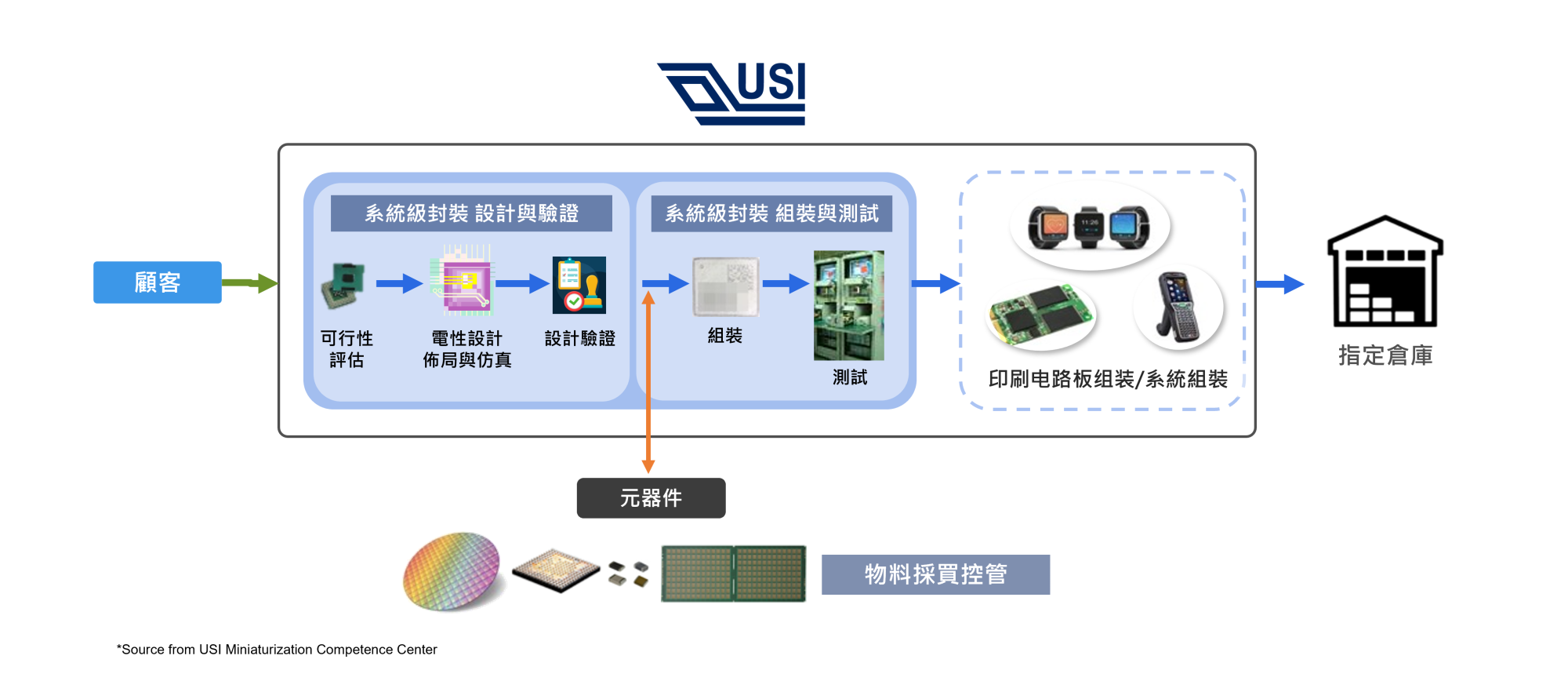

一站式系統級封裝服務

憑藉超過10年的系統級封裝經驗,環旭電子至今不僅僅在關鍵製程取得突破,我們已經能為客戶提供「一站式系統級封裝服務」。從電子/射頻的SiP設計、板端及模組的模擬驗證、封裝製程、系統級測試,甚至包含物料管控與將成品送達指定倉儲,完整滿足客戶的多樣化需求。

延伸閱讀:【5G後盾 全球發力】你不可不知的5G產品開發兩大挑戰!一站式5G射頻測試鏈助攻

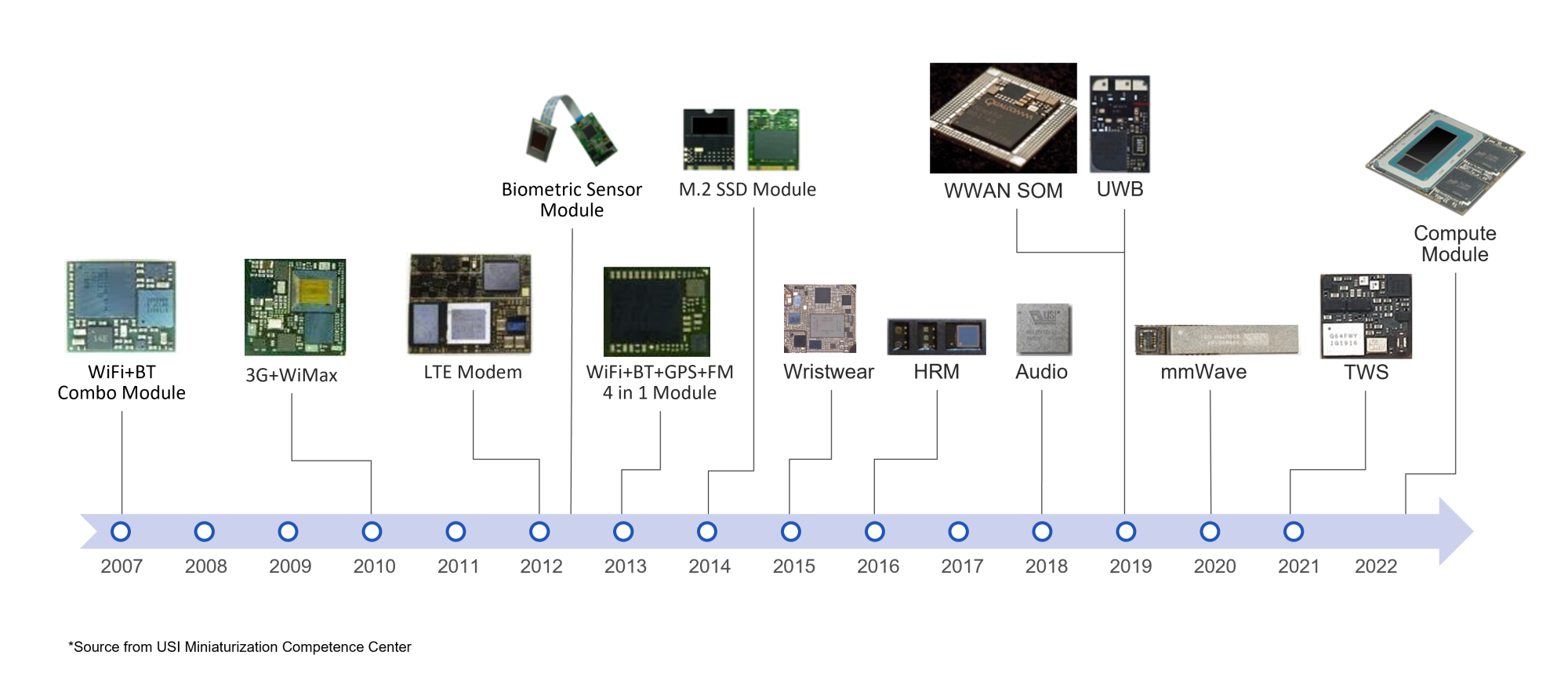

USI環旭電子微小化製造經驗 – 應用產品

面對客戶在系統級封裝產品的設計需求,環旭電子具備完整的資料庫,可在整體微小化的基礎上,提供料件及設計的最佳解,接著開始進行電路佈局(Layout) 與構裝(Structure)設計。經過封裝技術,將整體電路及子系統塑封在一個僅僅「晶片」大小的模組。

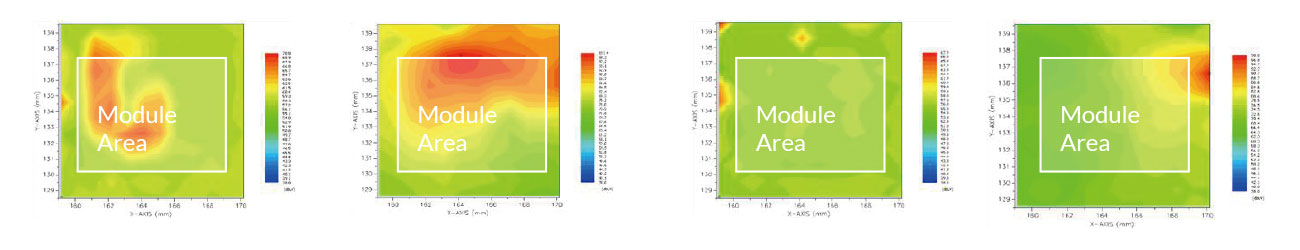

高密度與高整合的模組化設計前期的模擬與驗證特別至關重要,環旭電子提供包含載板設計和翹曲模擬、電源/訊號完整性分析(PI/SI)、熱流模擬分析(Thermal)等服務確保模組設計品質。實驗室內同時也已經為系統整合驗證建置完整設備,協助客戶進行模組打件至主板後的射頻校準測試與通訊協定驗證,並提供系統級功能性與可靠度驗證。

延伸閱讀:【5G後盾 全球發力】通訊協定開發及驗證,成就優質5G產品的最後一哩路

SiP模組可靠度及失效分析

由於內部線路和基板之間的複雜連結,當模組出現問題時,分析微米級元件的異常變得特別具有挑戰性,尤其是在電性測試期間,其他部件的導電性會影響測定結果。而且某些異常污染可能僅僅只有幾奈米的厚度,如:氧化或微侵蝕,使用一般的光學或電子顯微鏡根本無法發現。為了將製程問題降至最低,環旭電子在SiP模組失效分析領域持續強化分析能力,以X射線檢測(3D X–ray)、材料表面元素分析(XPS) 及傅立葉紅外線光譜儀(FTIR)等三大品管儀器找出解決之道:

失效分析三步驟

- X射線檢測(3D X–ray):透過失效分析當中的X–ray檢測,我們可以深入確認模組是否有封裝異常,並且找出異常元件的位置。

- 材料表面元素分析(XPS):接著,利用XPS針對微米等級的模組表面進行更細微的元素分析,以此探究模組出現電阻值偏高、電性異常、植球脫球及鍍膜脫層等現象是否來自於製程的氧化或汙染。

- 傅立葉紅外線光譜儀(FTIR):如明確查找到汙染物標的,則可再接續使用FTIR進行有機汙染物的鑑定,定義出問題根源究竟是來自哪一個階段,以此找出正確解決方案。

突破「微小化」競爭格局

憑藉異質整合微小化優勢,系統級封裝能集成不同製程技術節點 (technology node),不同功能、不同供應商,甚至是不同半導體原材料的元件,整體可為產品節省約30-40%的空間,也能依據需求客製模組外型並一定程度簡化系統主板設計,讓主板、天線及機構的設計整合上更加有彈性。同時,相較於IC製程的開發限制,系統整合模組可以在系統等級功能就先進行驗證與認證,加速終端產品開發,集中系統產品研發資源。

SiP技術是全球封測業者最看重的焦點,系統級封裝(SiP)技術的突破正在影響產業供應鏈、改變競爭格局。環旭電子從Wi-Fi模組產品就開始進行佈局、站穩腳步,積累多年在射頻、穿戴式裝置等產品的豐富製程經驗,透過「一站式系統級封裝服務」協助客戶實現構想。

《本文摘錄自環旭電子微小化創新研發中心產品副處長黃信榮NEPCON演說內容 – 2022.06.30》

跟緊產業脈動

隨時掌握第一手產業創新科技、應用與深度新聞

訂閱 USI 部落格

隨時掌握第一手產業創新科技、應用與深度新聞